Contenido

- Definición: ¿Qué significa el caché de nivel 1 (caché L1)?

- Una introducción a Microsoft Azure y la nube de Microsoft | A lo largo de esta guía, aprenderá de qué se trata la computación en la nube y cómo Microsoft Azure puede ayudarlo a migrar y administrar su negocio desde la nube.

- Techopedia explica el caché de nivel 1 (caché L1)

Definición: ¿Qué significa el caché de nivel 1 (caché L1)?

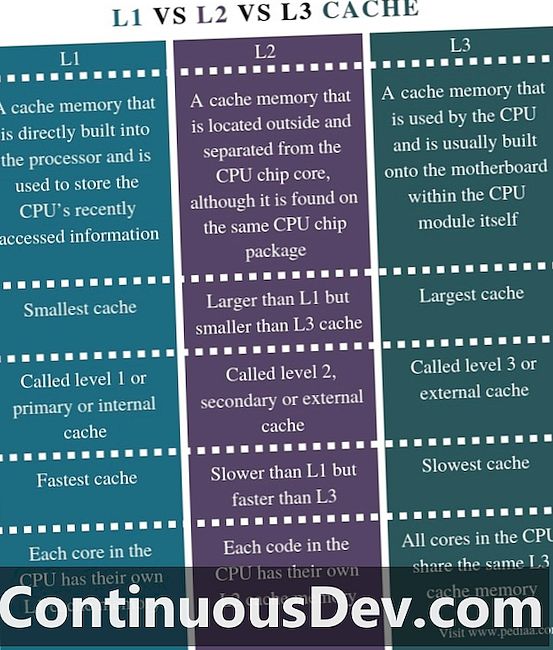

Un caché de nivel 1 (caché L1) es un caché de memoria que se integra directamente en el microprocesador, que se utiliza para almacenar la información a la que se accedió recientemente, por lo que también se denomina caché principal. También se conoce como caché interna o caché del sistema.

La memoria caché L1 es la memoria caché más rápida, ya que está construida dentro del chip con una interfaz de estado de espera cero, lo que la convierte en la memoria caché más costosa entre las memorias caché de la CPU. Sin embargo, tiene un tamaño limitado. Se utiliza para almacenar datos a los que el procesador accedió recientemente, archivos críticos que deben ejecutarse de inmediato y es la primera caché a la que se accede y procesa cuando el propio procesador realiza una instrucción de computadora.

Una introducción a Microsoft Azure y la nube de Microsoft | A lo largo de esta guía, aprenderá de qué se trata la computación en la nube y cómo Microsoft Azure puede ayudarlo a migrar y administrar su negocio desde la nube.

Techopedia explica el caché de nivel 1 (caché L1)

En microprocesadores más recientes, la memoria caché L1 se divide por igual en dos: una memoria caché que se usa para guardar los datos del programa y otra memoria caché que se usa para guardar las instrucciones para el microprocesador. Algunos microprocesadores más antiguos, por otro lado, hacen uso del caché L1 no dividido y lo usa para almacenar datos del programa e instrucciones del microprocesador.

Se implementa con el uso de memoria estática de acceso aleatorio (SRAM), que viene en diferentes tamaños según el grado del procesador. Esta SRAM utiliza dos transistores por bit. Los dos transistores forman un circuito conocido como flip-flop, ya que tiene dos estados entre los que puede cambiar; el segundo transistor gestiona la salida del primer transistor. Mientras se suministre energía al circuito, puede almacenar datos sin asistencia externa.

Todos los diseños de caché L1 siguen el mismo proceso; La lógica de control de la memoria caché L1 almacena los datos de uso frecuente en la memoria caché y solo actualiza la memoria externa cuando la CPU transfiere el control a otros maestros de bus cuando los dispositivos periféricos acceden directamente a la memoria.