Contenido

- Definición: ¿Qué significa la DRAM sincrónica (SDRAM)?

- Una introducción a Microsoft Azure y la nube de Microsoft | A lo largo de esta guía, aprenderá de qué se trata la computación en la nube y cómo Microsoft Azure puede ayudarlo a migrar y administrar su negocio desde la nube.

- Techopedia explica la DRAM Sincrónica (SDRAM)

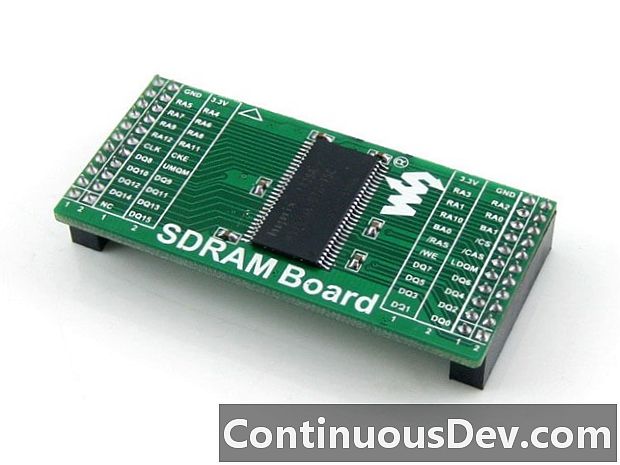

Definición: ¿Qué significa la DRAM sincrónica (SDRAM)?

La memoria de acceso aleatorio dinámico sincrónico (SDRAM) es una memoria de acceso aleatorio dinámico (DRAM) con una interfaz sincrónica con el bus del sistema que transporta datos entre la CPU y el concentrador del controlador de memoria. SDRAM tiene una interfaz síncrona de respuesta rápida, que está sincronizada con el bus del sistema. SDRAM espera la señal del reloj antes de responder a las entradas de control.

SDRAM precedió a la velocidad de datos doble (DDR). La interfaz más nueva de DRAM tiene una velocidad de transferencia de datos doble que utiliza los bordes ascendente y descendente de la señal del reloj. Esto se llama doble bombeo, doble bombeo o doble transición. Hay tres características significativas que diferencian SDRAM y DDR:

- La principal diferencia es la cantidad de datos transmitidos con cada ciclo, no la velocidad.

- SDRAM s señala una vez por ciclo de reloj. DDR transfiere datos dos veces por ciclo de reloj. (Tanto SDRAM como DDR usan las mismas frecuencias).

- SDRAM usa un borde del reloj. DDR usa ambos bordes del reloj.

SDRAM tiene un módulo de 64 bits con módulos de memoria dual en línea (DIMM) largos de 168 pines. El tiempo de acceso a SDRAM es de 6 a 12 nanosegundos (ns). SDRAM es el reemplazo de la memoria de acceso aleatorio dinámico (DRAM) y EDO RAM. DRAM es un tipo de memoria de acceso aleatorio (RAM) que tiene cada bit de datos en un componente aislado dentro de un circuito integrado. EDO RAM anterior realizada a 66 MHz.

Una introducción a Microsoft Azure y la nube de Microsoft | A lo largo de esta guía, aprenderá de qué se trata la computación en la nube y cómo Microsoft Azure puede ayudarlo a migrar y administrar su negocio desde la nube.

Techopedia explica la DRAM Sincrónica (SDRAM)

Con los circuitos electrónicos con reloj más antiguo, la velocidad de transferencia era de uno por ciclo completo de la señal del reloj. Este ciclo se llama ascenso y descenso. Una señal de reloj cambia dos veces por transferencia, pero las líneas de datos cambian no más de una vez por transferencia. Esta restricción puede causar integridad (corrupción de datos y errores durante la transmisión) cuando se utilizan anchos de banda altos. SDRAM transmite señales una vez por ciclo de reloj. El DDR más nuevo transmite dos veces por ciclo de reloj.

SDRAM es una DRAM mejorada con una interfaz síncrona que espera un pulso de reloj antes de responder a la entrada de datos. SDRAM utiliza una función llamada canalización, que acepta datos nuevos antes de terminar de procesar datos anteriores. Un retraso en el procesamiento de datos se llama latencia.

La tecnología DRAM se ha utilizado desde la década de 1970. En 1993, Samsung implementó SDRAM con la DRAM síncrona modelo KM48SL2000. En 2000, DRAM fue reemplazado por SDRAM. Al principio, SDRAM era más lento que la ráfaga EDO DRAM debido a las características lógicas adicionales. Pero los beneficios de SDRAM permitieron más de un conjunto de memoria, lo que aumentó la eficiencia del ancho de banda.

Con la introducción de DDR, SDRAM comenzó a desaparecer rápidamente porque DDR era más barato y más rentable. La SDRAM usó 168 pines, mientras que el módulo DDR usó 184 pines. Los módulos SDRAM usaron un voltaje de 3.3V y DDR usó 2.6V, produciendo menos calor.